行業動態

專注于半導體電性能測試

專注于半導體電性能測試

數字化轉型提速,5G 、人工智能及云端高性能算法(AI/HPC)的應用帶動集成電路(Integrated Circuit, IC)技術不斷升級,芯片電路結構復雜程度和元件集成度持續增加,測試難度和測試成本亦隨之攀升。

集成電路測試貫穿了從設計、生產到實際應用的全過程,大致分為:

- 設計階段的設計驗證測試

- 晶圓制造階段的工藝監控測試

- 封裝前的晶圓測試

- 封裝后的成品測試

芯片測試應用現狀

芯片測試作為芯片設計、生產、封裝、測試流程中的重要步驟,是使用特定儀器,通過對待測器件DUT(Device Under Test)的檢測,區別缺陷、驗證器件是否符合設計目標、分離器件好壞的過程。其中直流參數測試是檢驗芯片電性能的重要手段之一,常用的測試方法是FIMV(加電流測電壓)及FVMI(加電壓測電流)。

傳統的芯片電性能測試需要數臺儀表完成,如電壓源、電流源、萬用表等,然而由數臺儀表組成的系統需要分別進行編程、同步、連接、測量和分析,過程復雜又耗時,又占用過多測試臺的空間,而且使用單一功能的儀表和激勵源還存在復雜的相互間觸發操作,有更大的不確定性及更慢的總線傳輸速度等缺陷,無法滿足高效率測試的需求。

實施芯片電性能測試的最佳工具之一是數字源表(SMU),數字源表可作為獨立的恒壓源或恒流源、電壓表、電流表和電子負載,支持四象限功能,可提供恒流測壓及恒壓測流功能,可簡化芯片電性能測試方案。

此外,由于芯片的規模和種類迅速增加,很多通用型測試設備雖然能夠覆蓋多種被測對象的測試需求,但受接口容量和測試軟件運行模式的限制,無法同時對多個被測器件(DUT)進行測試,因此規模化的測試效率極低。特別是在生產和老化測試時,往往要求在同一時間內完成對多個DUT的測試,或者在單個DUT上異步或者同步地運行多個測試任務。

基于普賽斯CS系列多通道插卡式數字源表搭建的測試平臺,可進行多路供電及電參數的并行測試,高效、精確地對芯片進行電性能測試和測試數據的自動化處理。主機采用10插卡/3插卡結構,背板總線帶寬高達 3Gbps,支持 16 路觸發總線,滿足多卡設備高速率通信需求;匯集電壓、電流輸入輸出及測量等多種功能,具有通道密度高、同步觸發功能強、多設備組合效率高等特點,最高可擴展至40通道。

圖1:普賽斯CS系列插卡式源表

(10插卡及3插卡,高至40通道)

基于數字源表SMU的芯片測試方案

使用普賽斯數字源表進行芯片的開短路測試(Open/Short Test)、漏電流測試(Leakage Test)以及DC參數測試(DC Parameters Test)。

1、開短路測試(O/S測試)

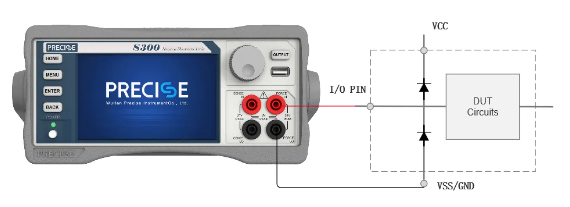

開短路測試(Open-Short Test,也稱連續性或接觸測試),用于驗證測試系統與器件所有引腳的電接觸性,測試的過程是借用對地保護二極管進行的,測試連接電路如下所示:

圖2:開短路測試線路連接示意

2、漏電流測試

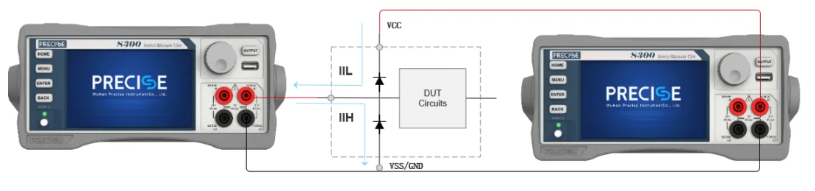

漏電流測試,又稱為Leakage Test,漏電流測試的目的主要是檢驗輸入Pin腳以及高阻狀態下的輸出Pin腳的阻抗是否夠高,測試連接電路如下所示:

圖3:漏電流測試線路連接示意

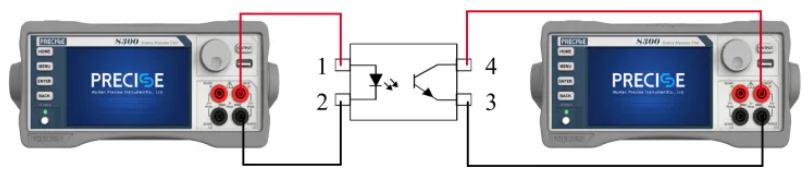

3、DC參數測試

DC參數的測試,一般都是Force電流測試電壓或者Force電壓測試電流,主要是測試阻抗性。一般各種DC參數都會在Datasheet里面標明,測試的主要目的是確保芯片的DC參數值符合規范:

圖4:DC參數測試線路連接示意

測試案例

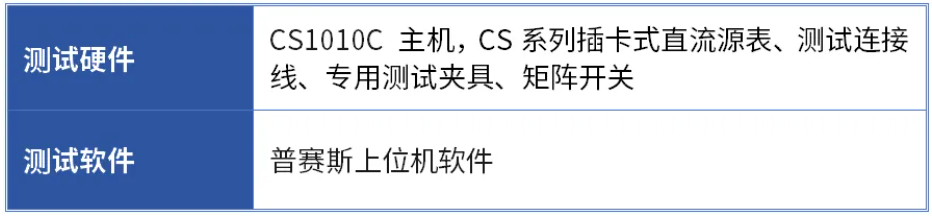

測試系統配置

Case 01 NCP1377B 開短路測試

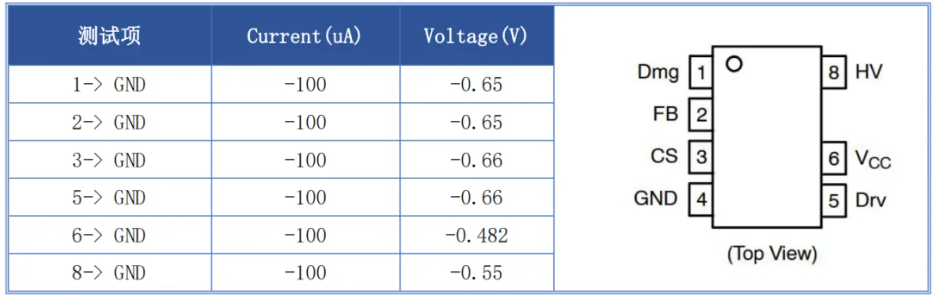

測試 PIN 腳與 GND 之間連通狀態,測試過程中SMU選擇3V量程,施加-100μA電流,限壓-3V,測量電壓結果表 1 所示,電壓結果在-1.5~-0.2 之間,測試結果 PASS。

*測試線路連接參照圖2

圖5:NCP1377B開短路測試結果

Case 02 TLP521 光電耦合器直流參數測試

光電耦合器主要由兩部分組成:光的發射端及光的接收端。光的發射端主要由發光二極管構成,二極管的管腳為光耦的輸入端。光的接收端主要是光敏晶體管, 光敏晶體管是利用 PN 結在施加反向電壓時,在光線照射下反向電阻由大變小的原理來工作的,晶體管的管腳為光耦的輸出端。

案例采用兩臺SMU進行測試,一臺SMU與器件輸入端連接,作為恒流源驅動發光二極管并測量輸入端相關參數,另一臺SMU與器件輸出端連接,作為恒壓源并測量輸出端的相關參數。

*測試線路連接參照圖4

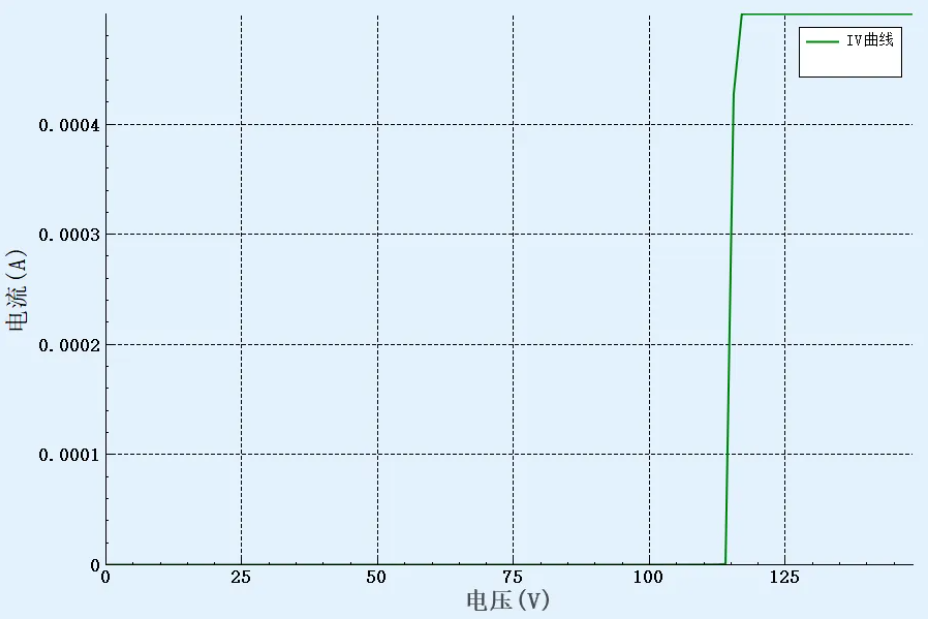

圖6:BVECO 測試數據及曲線

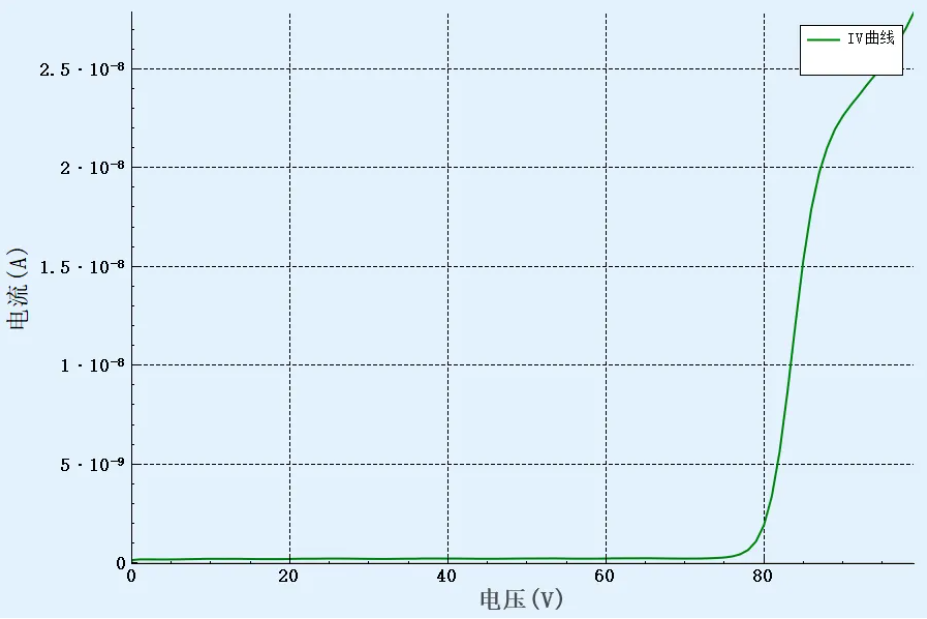

圖7:ICEO測試數據及曲線

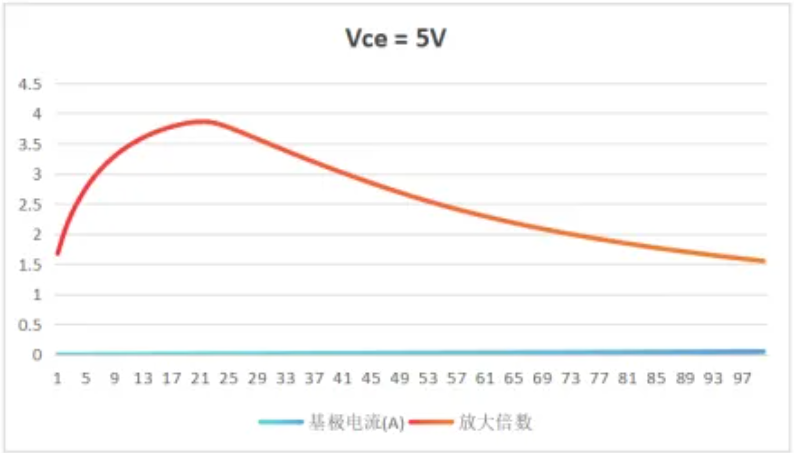

圖8:輸入特性曲線

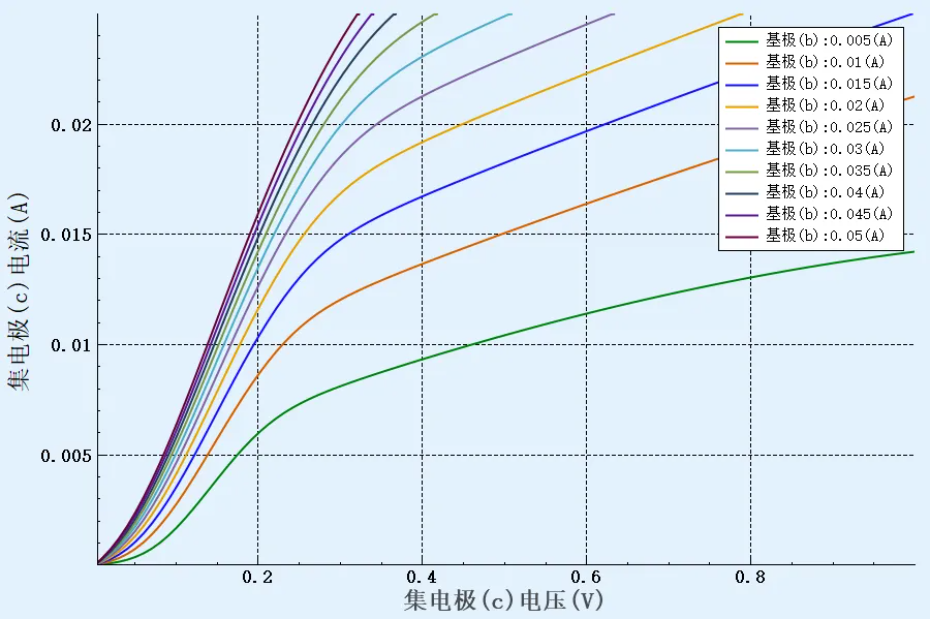

圖9:輸出特性曲線

在線

在線 咨詢

咨詢 掃碼

掃碼 下載

下載